### **Introduction to Semiconductor Devices**

### For Computing and Telecommunications Applications

From semiconductor fundamentals to state-of-the-art semiconductor devices used in the telecommunications and computing industries, this book provides a solid grounding in the most important devices used in the hottest areas of electronic engineering today. The book includes coverage of future approaches to computing hardware and RF power amplifiers, and explains how emerging trends and system demands of computing and telecommunications systems influence the choice, design, and operation of semiconductor devices.

The book begins with a discussion of the fundamental properties of semiconductors. Next, state-of-the-art field effect devices are described, including MODFETs and MOSFETs. Short channel effects and the challenges faced by continuing miniaturization are then addressed. The rest of the book discusses the structure, behavior, and operating requirements of semiconductor devices used in lightwave and wireless telecommunications systems.

This is both an excellent senior/graduate text, and a valuable reference for engineers and researchers in the field.

**Kevin Brennan** (1956–2003) was the recipient of a National Science Foundation Presidential Young Investigator Award. He was named School of ECE Distinguished Professor at Georgia Tech in 2002, and awarded a special commendation from the Vice Provost for Research in recognition of his contributions to graduate-level education in 2002. In 2003, he received the highest honor that a Georgia Tech faculty member can attain: the Class of 1934 Distinguished Professor Award. He also served as an IEEE Electron Device Society Distinguished Lecturer.

# Introduction to Semiconductor Devices

For Computing and Telecommunications Applications

KEVIN F. BRENNAN

CAMBRIDGE UNIVERSITY PRESS

Cambridge, New York, Melbourne, Madrid, Cape Town, Singapore, São Paulo, Delhi, Dubai, Tokyo, Mexico City

Cambridge University Press The Edinburgh Building, Cambridge CB2 8RU, UK

Published in the United States of America by Cambridge University Press, New York

www.cambridge.org

Information on this title: www.cambridge.org/9780521153614

© Cambridge University Press 2005

This publication is in copyright. Subject to statutory exception and to the provisions of relevant collective licensing agreements, no reproduction of any part may take place without the written permission of Cambridge University Press.

First published 2005 Reprinted 2006 First paperback printing 2010

A catalogue record for this publication is available from the British Library

ISBN 978-0-521-83150-5 Hardback ISBN 978-0-521-15361-4 Paperback

Cambridge University Press has no responsibility for the persistence or accuracy of URLs for external or third-party Internet Web sites referred to in this publication, and does not guarantee that any content on such Web sites is, or will remain, accurate or appropriate.

To my family, Lea, Casper, and Jack

# **Contents**

|       | Pretace                                                    | page x1 |

|-------|------------------------------------------------------------|---------|

|       | List of physical constants                                 | XV      |

|       | List of materials parameters for important semiconductors, |         |

|       | Si and GaAs                                                | xvi     |

| 1     | Semiconductor fundamentals                                 | 1       |

| 1.1   | Definition of a semiconductor                              | 2       |

| 1.2   | Equilibrium carrier concentrations and intrinsic material  | 7       |

| 1.3   | Extrinsic material                                         | 16      |

|       | Problems                                                   | 21      |

| 2     | Carrier action                                             | 23      |

| 2.1   | Drift and diffusion                                        | 23      |

| 2.2   | Generation-recombination                                   | 28      |

| 2.3   | Continuity equation and its solution                       | 33      |

|       | Problems                                                   | 36      |

| 3     | Junctions                                                  | 38      |

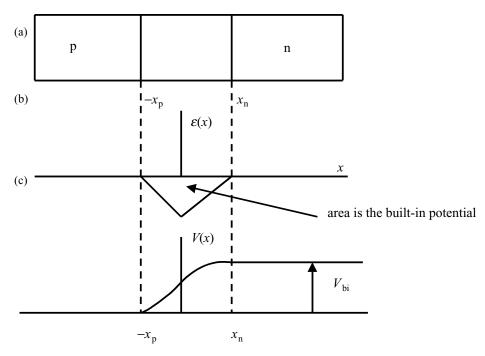

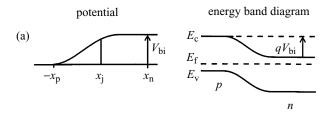

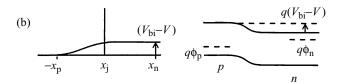

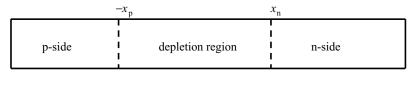

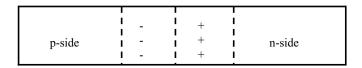

| 3.1   | p–n homojunction in equilibrium                            | 38      |

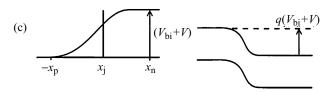

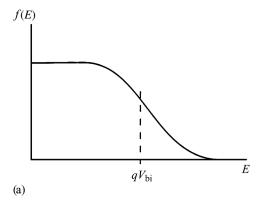

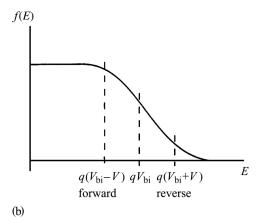

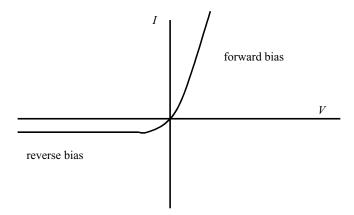

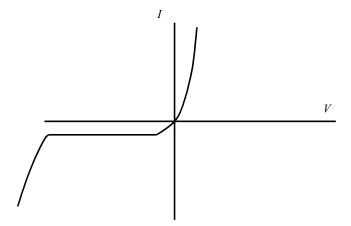

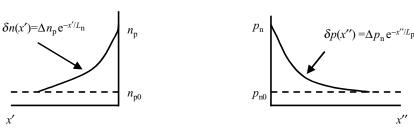

| 3.2   | p-n homojunctions under bias                               | 47      |

| 3.3   | Deviations from ideal diode behavior                       | 57      |

| 3.4   | Carrier injection, extraction, charge control analysis,    |         |

|       | and capacitance                                            | 61      |

| 3.5   | Schottky barriers                                          | 68      |

|       | Problems                                                   | 75      |

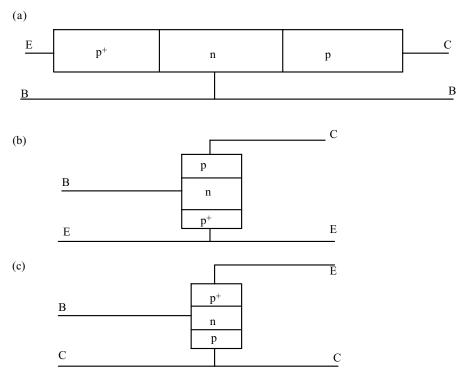

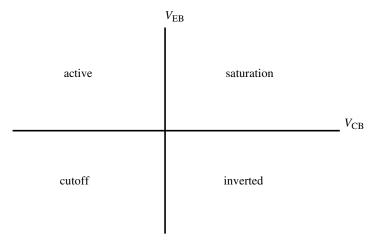

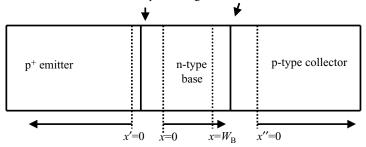

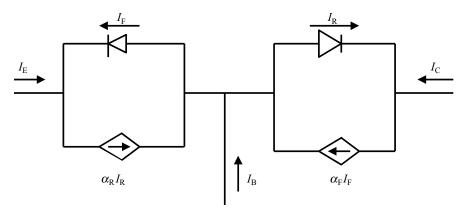

| 4     | Bipolar junction transistors                               | 78      |

| 4.1   | BJT operation                                              | 78      |

| 4.2   | Secondary effects in BJTs                                  | 92      |

| 4.2.1 | Drift in the base region                                   | 92      |

| 4.2.2 | Base narrowing or the Early Effect                         | 94      |

| 4.2.3 | Avalanche breakdown                                        | 95      |

| 4.3   | High frequency operation of a BJT                          | 97      |

|       | Problems                                                   | 99      |

## viii Contents

| 5    | JFETs and MESFETs                                        | 101 |

|------|----------------------------------------------------------|-----|

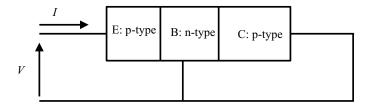

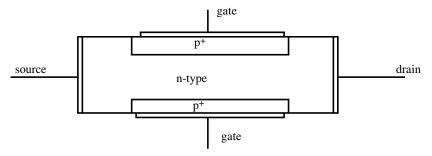

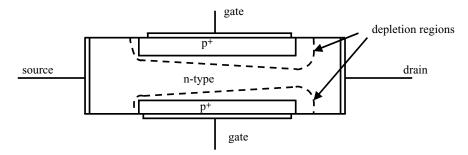

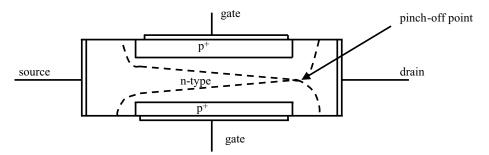

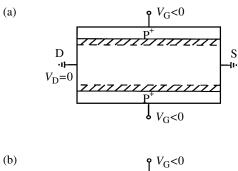

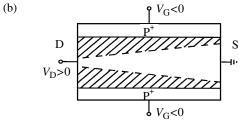

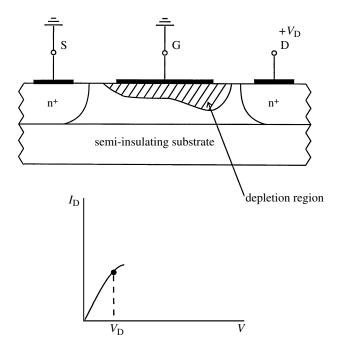

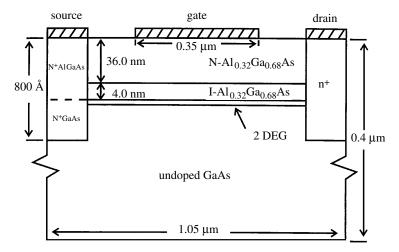

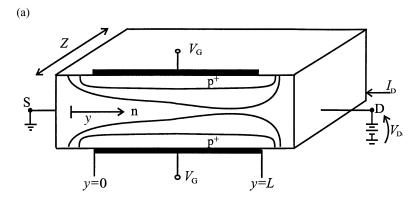

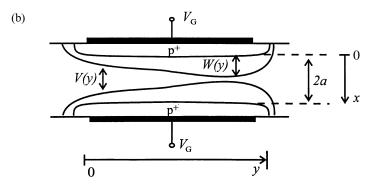

| 5.1  | JFET operation                                           | 101 |

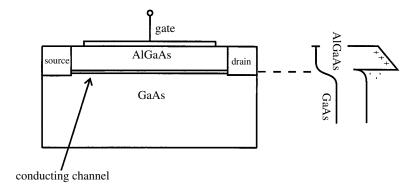

| 5.2  | MESFET and MODFET operation                              | 104 |

| 5.3  | Quantitative description of JFETs and MESFETs            | 112 |

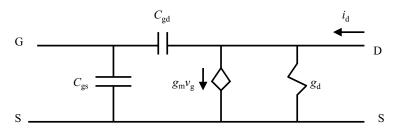

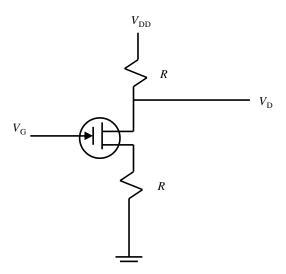

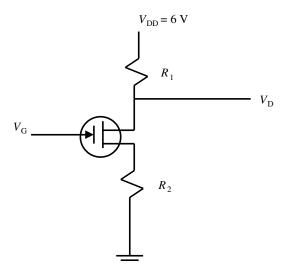

| 5.4  | Small signal model for a JFET                            | 121 |

|      | Problems                                                 | 124 |

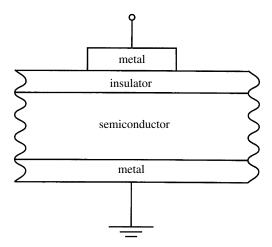

| 6    | Metal-insulator-semiconductor structures                 |     |

| U    | and MOSFETS                                              | 127 |

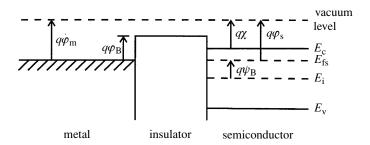

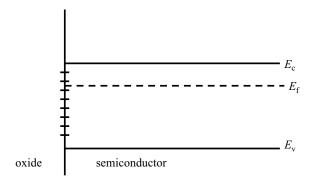

| 6.1  | MIS systems in equilibrium                               | 127 |

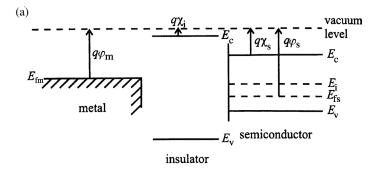

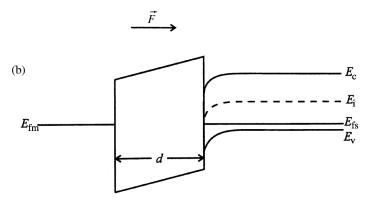

| 6.2  | MIS systems under bias                                   | 133 |

| 6.3  | Basic theory of MOSFET operation                         | 144 |

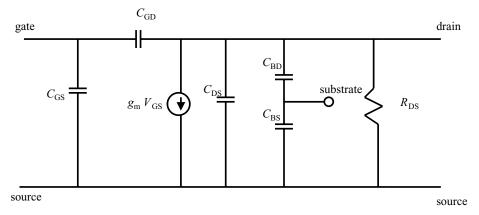

| 6.4  | Small signal operation of MESFETs and MOSFETs            | 155 |

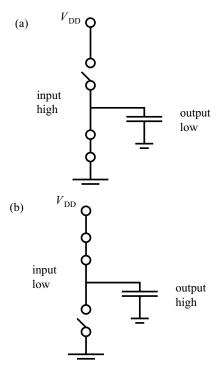

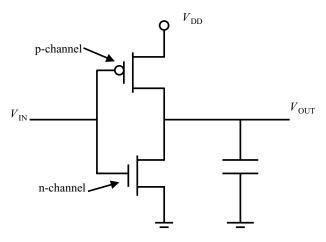

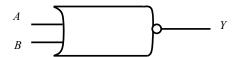

| 6.5  | CMOS circuits                                            | 160 |

|      | Problems                                                 | 165 |

| 7    | Short-channel effects and challenges to CMOS             | 169 |

| 7.1  | Short-channel effects                                    | 169 |

| 7.2  | Scaling theory                                           | 176 |

| 7.3  | Processing challenges to further CMOS miniaturization    | 183 |

|      | Problems                                                 | 186 |

| 8    | Beyond CMOS                                              | 188 |

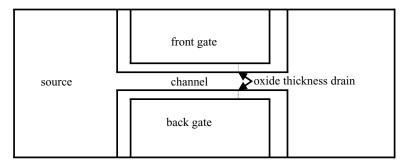

| 8.1  | Evolutionary advances beyond CMOS                        | 188 |

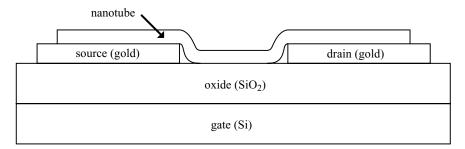

| 8.2  | Carbon nanotubes                                         | 195 |

| 8.3  | Conventional vs. tactile computing, molecular and        |     |

|      | biological computing                                     | 197 |

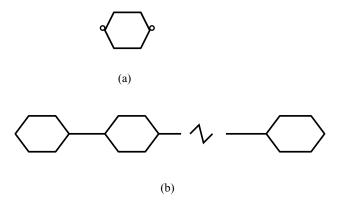

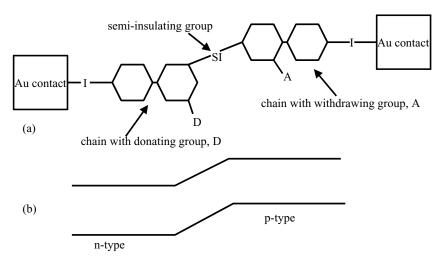

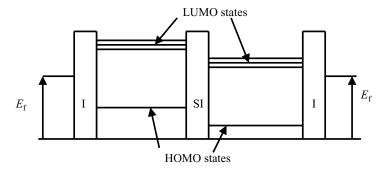

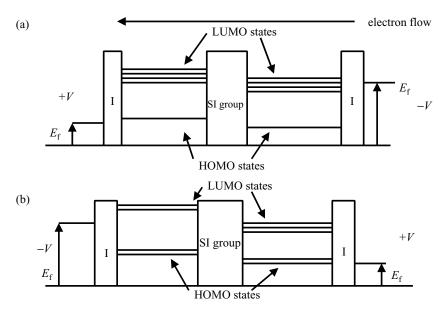

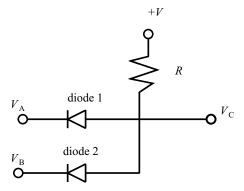

| 8.4  | Moletronics – molecular diodes and diode–diode logic     | 201 |

| 8.5  | Defect tolerant computing                                | 206 |

| 8.6  | Quantum dot cellular automata                            | 210 |

|      | Problems                                                 | 219 |

| 9    | Telecommunications systems – an overview                 | 220 |

| 9.1  | Fiber transmission                                       | 220 |

| 9.2  | Amplifiers and repeaters                                 | 223 |

| 9.3  | Mobile cellular telecommunications systems               | 225 |

| 9.4  | Device types for cellular systems                        | 228 |

| 10   | Optoelectronic devices – emitters, light amplifiers, and |     |

|      | detectors                                                | 230 |

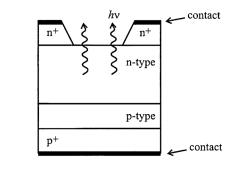

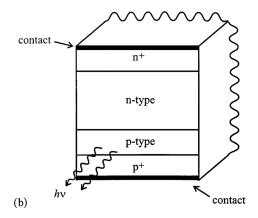

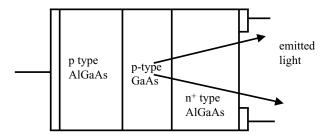

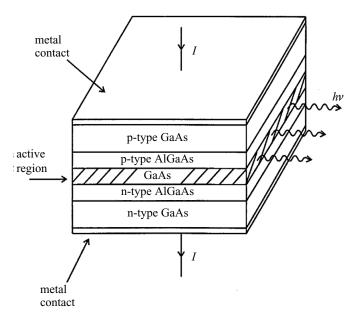

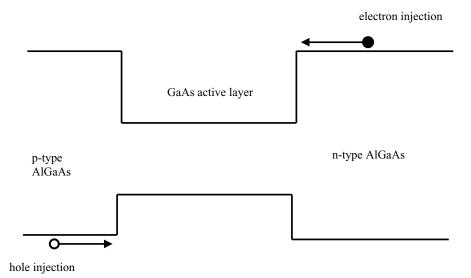

| 10.1 | LEDs                                                     | 230 |

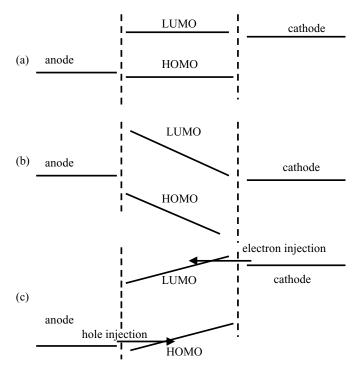

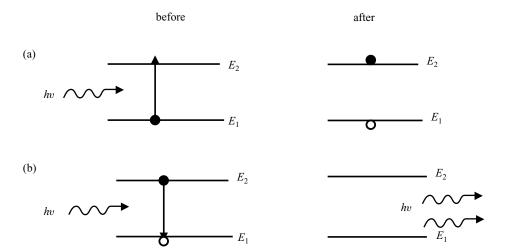

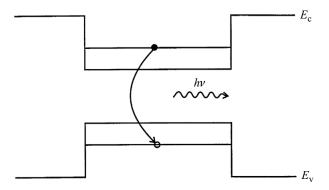

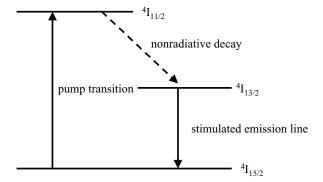

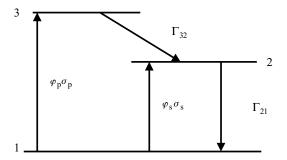

| 10.2 | Stimulated emission                                      | 238 |

| 10.3 | Laser operation                                          | 244 |

|      |                                                  | Contents | ix |

|------|--------------------------------------------------|----------|----|

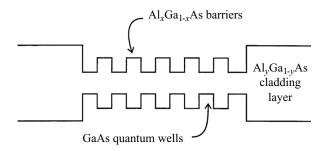

| 10.4 | Types of semiconductor lasers                    | 248      |    |

| 10.5 | EDFAs                                            | 255      |    |

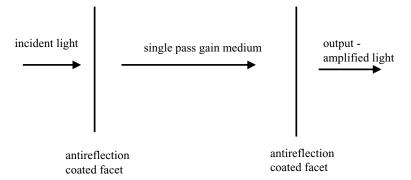

| 10.6 | SOAs                                             | 258      |    |

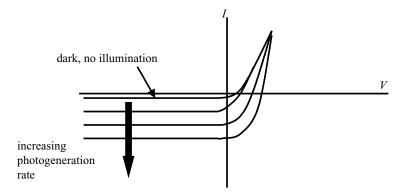

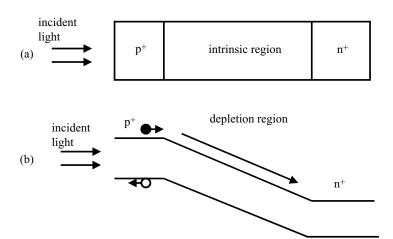

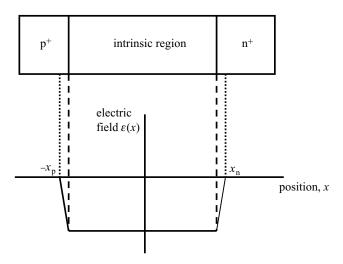

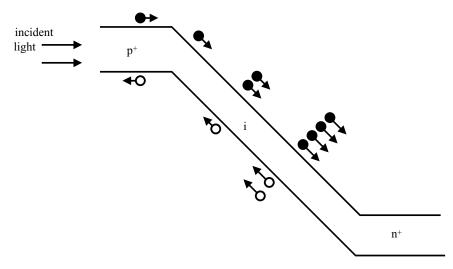

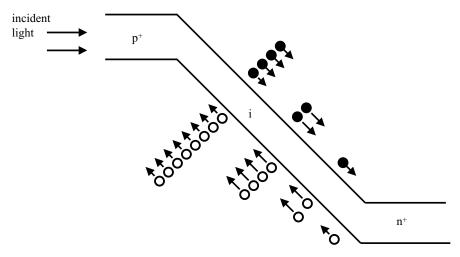

| 10.7 | p—i—n photodetectors                             | 260      |    |

| 10.8 | Avalanche photodiodes                            | 265      |    |

|      | Problems                                         | 273      |    |

| 11   | Transistors for high frequency, high power       |          |    |

|      | amplifiers for wireless systems                  | 275      |    |

| 11.1 | Transistor figures of merit for wireless systems | 275      |    |

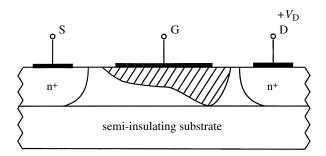

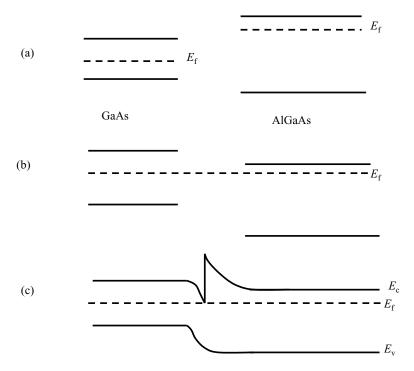

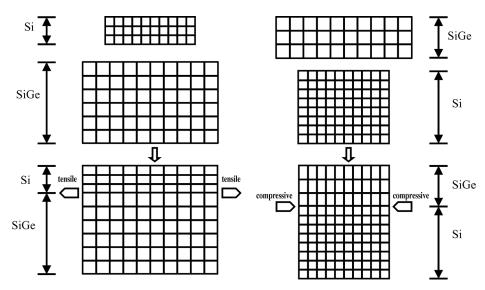

| 11.2 | Heterostructures                                 | 281      |    |

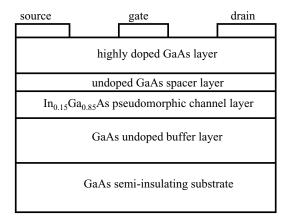

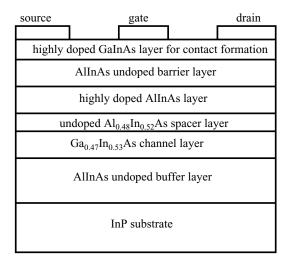

| 11.3 | MODFET devices                                   | 286      |    |

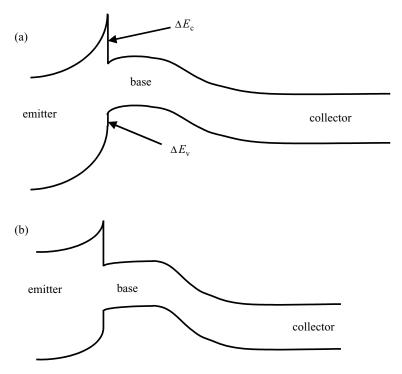

| 11.4 | HBTs                                             | 290      |    |

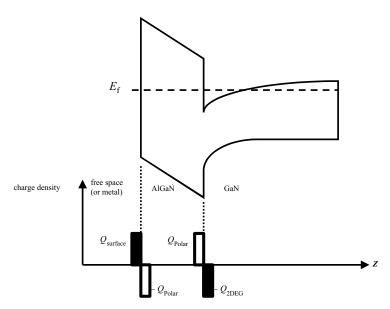

| 11.5 | Wide band gap semiconductors                     | 294      |    |

|      | Problems                                         | 298      |    |

|      | References                                       | 300      |    |

|      | Index                                            | 303      |    |

# **Preface**

At the time of this writing the microelectronics industry is poised at the threshold of a major turning point. For nearly fifty years, the industry has grown from the initial invention of the integrated circuit through the continued refinement and miniaturization of silicon based transistors. Along with the development of complementary metal oxide semiconductor circuitry, miniaturization of semiconductor devices created what has been called the information revolution. Each new generation of devices leads to improved performance of memory and microprocessor chips at ever reduced cost, thus fueling the expansion and development of computing technology. The growth rate in integrated circuit technology, a doubling in chip complexity every eighteen months or so, is known as Moore's First Law. Interestingly, the semiconductor industry has been able to keep pace with Moore's First Law and at times exceed it over the past forty years. However, now at the beginning of the twenty-first century doubts are being raised as to just how much longer the industry can follow Moore's First Law. There are many difficult challenges that confront CMOS technology as device dimensions scale down below 0.1 µm. Many people have predicted that several of these challenges will be so difficult and expensive to overcome that continued growth in CMOS development will be threatened. Further improvement in device technology will then require a disruptive, revolutionary technology.

One might first wonder why is it important to continue to improve microprocessor speed and memory storage much beyond current levels? Part of the answer to this question comes from the simultaneous development of the telecommunications industry. Both lightwave communications and cellular communications systems have grown rapidly. Over just the past ten years, the cellular telephone industry has increased exponentially, making it one of the fastest growing industries in the world. The expansion of cellular telephony to the transmission of data, internet connections, and video information is already beginning. Cellular transmission of video information will require much higher bandwidth operation and greater sophistication than is currently available in cellular systems. Lightwave systems already handle video and internet communications and are pressed to improve bandwidth for faster operation. Though improvement in software and algorithms has been highly instrumental in improving telecommunications system capacity, hardware improvements are equally as important to maintain growth in these systems. Therefore, there is an acute need for faster electronics with a concurrent memory enhancement to improve telecommunications systems, thus further fueling the information revolution.

It is my opinion that the microelectronics industry will necessarily continue to grow to meet the demands of future computing and telecommunications systems.

However, this growth may not be confined to silicon CMOS but may extend into several other technologies as well. The goal of this book is to present an introductory discussion to undergraduate students of the basic workings of current semiconductor devices used in computing and telecommunications systems and to present some of the emerging revolutionary approaches that microelectronics could take in the near future. Throughout the book, the applications and operating requirements imposed on semiconductor hardware by computing and telecommunications applications are used to describe the important figures of merit of each device. In this way, the student can clearly see what fundamental properties a particular device must have to meet the system application requirements for which it is designed.

One might wonder why yet another book is needed on semiconductor devices for undergraduate education. This question is particularly relevant in that several universities have recently decided to abandon requiring an undergraduate course in semiconductor devices, making it solely an elective instead. Given that there are several excellent texts, such as Streetman and Banerjee Solid State Electronic Devices (2000) or Pierret Semiconductor Device Fundamentals (1996), one might wonder why another undergraduate book is needed especially in light of the fact that the need for undergraduate books is apparently decreasing. Though the above mentioned books are unquestionably excellent, they do not provide a discussion of the future of microelectronics and how it relates to the greatest existing growth industries of computing and telecommunications. It is the primary purpose of this book to provide the context, namely computing and telecommunications, in which semiconductor devices play their most important and ubiquitous role. Further, the present book provides a look at not only the state-of-the-art devices but also future approaches that go beyond current technology. In this way, a new, refreshing, up-to-date approach to teaching semiconductor devices and exciting the students about the future of the field is provided. It is my opinion that through an enlightened approach the negative trend of the removal of microelectronics courses from undergraduate curriculums can be reversed. Ironically, I believe that microelectronics is poised for its greatest surge. Thus rather than abandoning teaching microelectronics, it should be more widely presented and the approach should be more interdisciplinary at least addressing possibilities in molecular and biological systems for future computing hardware. This book presents a first cut at such an interdisciplinary approach.

This book has grown out of notes used for an undergraduate course I teach in the School of Electrical and Computer Engineering at Georgia Tech. The course is one semester long and follows a required course in circuit theory that includes some of the basics of semiconductor devices. However, the book does not draw on the student's knowledge of circuits and can thus be used as a first course in semiconductor devices. Given that the presentation is a bit briefer than most semiconductor device texts on the fundamentals, the book is probably better suited for either a second level course, as is done at Georgia Tech, or a first level course for more advanced students. As for scientific and mathematical background, the book requires knowledge of calculus and differential equations. However, no knowledge of quantum mechanics, solid state physics or statistical mechanics is required. Computer based assignments have not been

included in the text. The main reasons for their exclusion is that we are preparing a computer based exercise book for use in all of our undergraduate level microelectronics courses. The proposed book will have computer exercises that follow the present book providing another path for learning.

The present book is organized as follows. It begins with a presentation of the essential fundamentals of semiconductors. The second chapter discusses carrier action. The third chapter focuses on junctions including p-n homojunctions, Schottky barriers, and ohmic contacts. In the fourth chapter, bipolar junction transistors are presented. JFETs and MESFETs are discussed in Chapter 5, including ac models. Chapter 6 presents a discussion of metal insulator semiconductor systems particularly MOS devices, long channel MOSFETs, and CMOS circuits. Short channel devices, scaling and challenges to further improvement of CMOS devices are discussed in Chapter 7. Chapter 8 presents a discussion of several different technical approaches that go beyond CMOS. The topics in Chapter 8 are limited to those that do not require knowledge of quantum mechanics. These topics are included in the graduate level textbook *Theory* of Modern Electronic Semiconductor Devices (2002) by Kevin F. Brennan and April S. Brown. The balance of the book focuses on device use in lightwave and cellular telecommunications systems. Chapter 9 gives an overview of telecommunications systems, both wired and wireless. In Chapter 10 a discussion of optoelectronic devices used in lightwave communications systems such as LEDs, lasers, erbium doped fiber amplifiers, semiconductor optical amplifiers and photodetectors is presented. The book concludes with a discussion of transistors used in high frequency, high power amplifiers such as MODFETs and HBTs in Chapter 11.

This book is designed to be the first in a series of texts written by the current author. It provides an introduction to semiconductor devices using only for the most part classical physics. Some limited discussion about spatial quantization is included, however. Thus the present book is well suited to the typical junior or senior level undergraduate student. After completing a course that utilizes the present book, the student is prepared for graduate level study. At Georgia Tech graduate students in microelectronics begin their study, following an undergraduate course at the level of the present book, with the basic science of quantum mechanics, statistical mechanics, and solid state physics covered in *The Physics of Semiconductors with Applications to Optoelectronic Devices* (1999), by Kevin F. Brennan. This material is covered in a first semester graduate level course that is followed by a second semester graduate level course on modern electronic devices. The textbook for the second semester graduate level course at Georgia Tech is *Theory of Modern Electronic Semiconductor Devices* (2002) by Kevin F. Brennan and April S. Brown.

Pedagogically, the undergraduate course this book has been developed from is taught three times a year at Georgia Tech. This course is a second level course in semiconductor devices that follows a required course that contains both circuit theory and elementary semiconductor material. Since the book is used at Georgia Tech for a second level course, we typically quickly cover the topics in Chapters 1–3 in about 2–3 weeks. Depending upon the student's preparation, the fourth chapter can be skipped, substituting a brief review instead. The course gets "down to business" beginning with

#### **xiv** Preface

Chapter 5 and goes through the remaining chapters for the balance of the semester. Often we skip the section on CMOS (this is covered in the circuits level course) as well as Chapter 9 which is generally just assigned reading. Homework problems are typically selected from those at the back of the chapters. Two in-class quizzes and a final examination are given. Instructors can obtain a solutions manual for the problems on-line at www.ece.gatech.edu/research/labs/comp\_elec. The solutions manual can be downloaded and is password protected. Instructors only are given access to the solutions. Please follow the directions at the web site to obtain the necessary password.

The author would like to thank his many colleagues and students at Georgia Tech that have provided constructive criticism in the writing of this book. Specifically, the author is thankful to Mike Weber for his help on some of the figures and for assisting in creating the book web site. Thanks go to Professor Wolfgang Porod of Notre Dame University and to Dr. Phaedron Avouris at IBM for granting permission to reproduce some of their work.

Finally, I would like to thank my family and friends for their enduring support and patience.

### **Postscript**

Professor Kevin Brennan, my colleague at Georgia Tech, and one of my best friends, passed away on August 2, 2003. After he became ill, he continued to work on this text during the last year of his life, and had essentially completed it at the time of his death. I became involved at the copy-editing stage, and would like to express my appreciation to his wife, Lea McLees, for allowing me to assist in bringing this text to conclusion. I would like to acknowledge the effort of Ms. Maureen Storey, whose meticulous attention to detail was essential to the completion of the project. Most of my corrections and additions were reactive to her questions and comments. Eric Willner at Cambridge University Press showed considerable patience in both coaxing us and allowing us time to polish the text. The Chair of the School of Electrical and Computer Engineering at Georgia Tech, Dr. Roger Webb, provided both emotional and tangible support during this difficult period. Professor Christiana Honsberg and Professor Tom Gaylord at Georgia Tech provided answers to questions from me at critical junctures. Kevin Brennan was a superb teacher, accomplished researcher, and prolific author. I am appreciative of the fact that he is able to teach us one last time.

Atlanta, GA March, 2004 W. Russell Callen

# **Physical constants**

| Avogadro's constant       | $N_{ m AVO}$    | $6.022 \times 10^{23}$  | $Mol^{-1}$        |

|---------------------------|-----------------|-------------------------|-------------------|

| Boltzmann's constant      | $k_{ m B}$      | $1.38 \times 10^{-23}$  | J/K               |

|                           |                 | $8.62 \times 10^{-5}$   | eV/K              |

| Electron charge           | q               | $1.6 \times 10^{-19}$   | C                 |

| Electron rest mass        | $m_0$           | $0.511 \times 10^6$     | eV/C <sup>2</sup> |

|                           |                 | $9.11 \times 10^{-31}$  | kg                |

| Permeability – free space | $\mu_0$         | $1.2566 \times 10^{-8}$ | H/cm              |

| Permittivity – free space | $\varepsilon_0$ | $8.85 \times 10^{-14}$  | F/cm              |

| Planck's constant         | h               | $4.14 \times 10^{-15}$  | eV s              |

|                           |                 | $6.63 \times 10^{-34}$  | Js                |

| Reduced Planck's constant | $\hbar$         | $6.58 \times 10^{-16}$  | eV s              |

|                           |                 | $1.055 \times 10^{-34}$ | Js                |

| Speed of light            | c               | $3.0 \times 10^{10}$    | cm/s              |

| Thermal voltage – 0300 K  | $k_{\rm B}T/q$  | 0.0259                  | V                 |

|                           |                 |                         |                   |

# Material parameters for important semiconductors, Si and GaAs

### **Bulk material parameters for silicon**

| Lattice constant (Å)                                               | a = 5.43              |

|--------------------------------------------------------------------|-----------------------|

| Dielectric constant                                                | 11.9                  |

| Intrinsic carrier concentration (cm <sup>-3</sup> )                | $1.0 \times 10^{10}$  |

| Energy band gap (eV)                                               | 1.12                  |

| Sound velocity (cm/s)                                              | $9.04 \times 10^{5}$  |

| Density (g cm <sup>-3</sup> )                                      | 2.33                  |

| Effective mass along $X(m^*/m_0)$ – transverse                     | 0.19                  |

| Effective mass along $X(m^*/m_0)$ – longitudinal                   | 0.916                 |

| Effective mass along $L(m^*/m_0)$ – transverse                     | 0.12                  |

| Effective mass along $L(m^*/m_0)$ – longitudinal                   | 1.59                  |

| Heavy hole mass $(m^*/m_0)$                                        | 0.537                 |

| Electron mobility at 300 K (cm <sup>2</sup> /(V s))                | 1450                  |

| Hole mobility at 300 K ( $cm^2/(V s)$ )                            | 500                   |

| Thermal conductivity at 300 K (W/(cm °C))                          | 1.5                   |

| Effective density of states in conduction band (cm <sup>-3</sup> ) | $2.8 \times 10^{19}$  |

| Effective density of states in valence band (cm <sup>-3</sup> )    | $1.04 \times 10^{19}$ |

| Nonparabolicity along $X$ (eV <sup>-1</sup> )                      | 0.5                   |

| Intravalley acoustic deformation potential (eV)                    | 9.5                   |

| Optical phonon energy at $\Gamma$ (eV)                             | 0.062                 |

| Intervalley separation energy, $X$ – $L$ (eV)                      | 1.17                  |

# **Bulk material parameters for GaAs**

| Lattice constant (Å)                                 | a = 5.65             |

|------------------------------------------------------|----------------------|

| Low frequency dielectric constant                    | 12.90                |

| High frequency dielectric constant                   | 10.92                |

| Energy band gap at 300 K (eV)                        | 1.425                |

| Intrinsic carrier concentration (cm <sup>-3</sup> )  | $2.1 \times 10^{6}$  |

| Electron mobility at 300 K (cm <sup>2</sup> /(V s))  | 8500                 |

| Hole mobility at $300 \text{ K (cm}^2/(\text{V s}))$ | 400                  |

| Longitudinal sound velocity (cm/s) along (100)       |                      |

| direction                                            | $4.73 \times 10^{5}$ |

| Density (g/cm <sup>3</sup> )                         | 5.36                 |

|                                                      |                      |

| 0.067              |

|--------------------|

| 0.56               |

| 0.85               |

| 0.62               |

| $4.7\times10^{17}$ |

| $7.0\times10^{18}$ |

| 0.46               |

| 0.690              |

| 8.0                |

| 0.035              |

| 0.284              |

| 0.476              |

|                    |

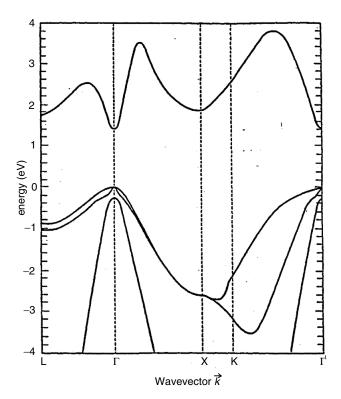

*Note*:  $\Gamma$  designates a point in k-space; X and L designate directions in k-space.  $\Gamma$  refers to the k=0 point at the center of the Brillouin zone. X refers to the  $\{100\}$  directions and L to the  $\{111\}$  directions.

# Semiconductor fundamentals

In this chapter, we review the basic fundamentals of semiconductors that will be used throughout the text. Only the fundamental issues that we will need to begin our study of semiconductor devices utilized in computing and telecommunications systems are discussed.

Before we begin our study it is useful to point out how semiconductor devices are instrumental in many applications. In this book we will mainly examine the application of semiconductor devices to computing and telecommunications systems. Specifically, we will examine the primary device used in integrated circuits for digital systems, the metal oxide semiconductor field effect transistor, MOSFET. The discussion will focus on state-of-the-art MOSFET devices and future approaches that extend conventional MOSFETs and revolutionary approaches that go well beyond MOSFETs. It is expected that computing hardware will continue to improve, providing faster and more powerful computers in the future using either some or all of the techniques discussed here or perhaps using completely new technologies. In any event, there is almost certainly going to be a large growth in computing hardware in order to maintain the pace of computer development and this book will help introduce the student to emerging technologies that may play a role in future computing platforms.

The second major topic of this book involves discussion of semiconductor devices for telecommunications applications. We will examine devices of use in lightwave communications as well as wireless communications networks. Among these devices are emitters, detectors, amplifiers, and repeaters.

Some mention should be made of the various commercial products that are and will be greatly impacted by semiconductor devices. The development of blue and blue-green light emitting diodes (LEDs) and lasers foments the evolution of new, highly efficient, rugged, ultra-long-life illumination elements. White light emitters using LEDs are now becoming commercially available. These emitters are far more efficient than incandescent bulbs, cost about the same or less, have lifetimes measured in years rather than months, are rugged and durable. It is expected that replacing incandescent lighting by LEDs worldwide can result in a substantial energy savings and potentially reduce consumption of fossil fuels. Perhaps this will lead to a reduction in greenhouse gas emission and help combat global warming and environmental decay in general. Blue lasers enable the development of very small compact discs for data storage, video and audio systems thus greatly expanding the storage capacity of CDs.

New semiconductor materials, such as gallium nitride (GaN) and silicon carbide (SiC), are emerging that are far more tolerant of high temperatures, and operate at significantly higher current densities and frequencies than existing devices. Devices

made from these materials are highly attractive for high power, high frequency, and high temperature operation. Specific applications are as power amplifiers for base stations in wireless telecommunications systems, hybrid electric vehicles, switching elements for electric power grids, and high power amplification for radar and satellite communications. Thus GaN and SiC may emerge as important semiconductor materials for many important applications.

#### 1.1 Definition of a semiconductor

The first question one might raise is why are semiconductor materials important in electrical engineering? To answer this question let us first consider a useful characterization scheme for solids based on their electrical properties, specifically their electrical conductivity. Generally, all crystalline solids can be classified into one of four categories. These categories, arranged from highest electrical conductivity to lowest, are metals, semimetals, semiconductors, and insulators. The distinction among these four categories is of course, somewhat vague. For instance, some materials can be either metallic or semimetallic depending upon the form into which they crystallize. Additionally, the distinction between semiconductors and insulators can often become blurred for the wide band gap materials. Nevertheless, we will find it convenient to classify solids into one of these four categories.

Of the four classes of materials, semiconductors are arguably the most important in electrical engineering. The principal reason underlying the importance of semiconductors is the fact that their electrical properties can be readily engineered. Semiconductors are unique in that their conductivity can be significantly altered in several different ways. For the other three types of solids, metals, semimetals, and insulators, their conductivity cannot be readily and significantly altered making them far less attractive for electrical engineering.

There are numerous ways in which the conductivity of a semiconductor can be altered. In this book, we will address most of these approaches and how they can be utilized to make useful semiconductor devices. Before we outline the approaches to manipulating the electrical conductivity of a semiconductor, we should first review what a semiconductor is.

The most commonly used semiconductors are the elemental semiconductors silicon and germanium, and the compound semiconductors, consisting of compound materials. There are numerous compound semiconductors but they are generally formed from two, three, or four different elements and are referred to as binary, ternary, and quaternary compounds respectively. The most important compound semiconductors are based on Column IIIA and Column VA elements in the Periodic Table. For this reason, these compounds are called the III–V compound semiconductors or III–Vs. Examples of the III–V compounds are gallium arsenide (GaAs), indium phosphide (InP), aluminum arsenide (AlAs), indium arsenide (InAs), etc. Notice that in each case the cation is a Column III element while the anion is a Column V element. Ternary compounds can be formed using three elements such as  $Al_xGa_{1-x}As$ , where the subscript x represents the mole fraction of aluminum present in the compound. Similarly,

quaternary compounds can be formed in which four elements are combined. An example of a quaternary compound semiconductor is  $In_xGa_{1-x}As_vP_{1-v}$ .

How though can we identify which materials are semiconductors? To answer this question we must first consider a fundamental result in the physics of solids. Every crystalline solid has translational symmetry. A system is said to have translational symmetry if it can be broken into a set of identical basic unit cells such that when the system is translated by a distance equal to the length of one unit cell it remains invariant. An obvious example is that of a uniform brick wall. If one translates a row of bricks by a length equal to that of a single brick, the wall looks precisely the same as before. The wall is said to be invariant under a linear translation. A similar situation holds for a crystalline solid. The arrangements of atoms forming a crystalline solid are like the bricks of a uniform wall. The atoms, much like the bricks, are arranged in periodic intervals. Therefore, when the system is translated by a distance equal to the separation between two adjacent atom centers, called the lattice constant, the system remains the same and is said to be invariant. Since the arrangement of the positions of the atoms in a crystalline solid is periodic, the electrostatic potential corresponding to the atoms is also periodic. The potential of the solid is thus also translationally symmetric. The fact that all crystalline solids have a periodic potential is extremely important. There is a fundamental result from quantum mechanics that applies to any system with a periodic potential. This result (Brennan, 1999, Chapter 8) states that for a system with a translationally symmetric potential, the electron energy levels are arranged in bands. These bands can either be conducting or forbidden. As the name implies a conduction band is one in which the electrons can propagate or conduct. Conversely, a forbidden band is one in which no conducting states exist. Electrons cannot be placed into a forbidden band.

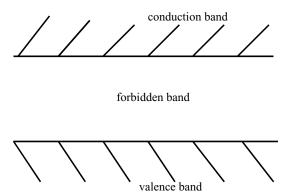

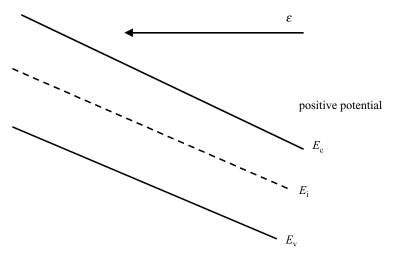

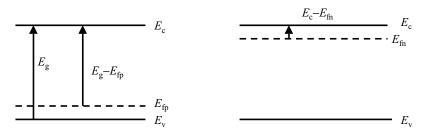

In addition to the formation of energy bands, the presence of a periodic potential introduces energy gaps in the allowed energy spectrum. These gaps are called forbidden gaps. Forbidden gaps correspond to energy ranges wherein no allowed electronic states exist. A typical diagram showing a valence band, forbidden energy band and conduction band is shown in Fig. 1.1. As can be seen from the figure, allowed energy states exist only within the conduction and valence energy bands. As mentioned above, electrons within the conduction band can propagate through the crystal and thus carry a current. Electrons cannot be located within the forbidden band. In the valence band, electronic states exist but these states are not free. In other words, electrons within the valence band are localized into bound states that are formed by the molecular bonds between the constituent host atoms of the crystal.

A completely empty band cannot conduct a current. This should be obvious since an empty band has no carriers within it and thus there is nothing to carry the current. A less obvious fact is that a completely filled energy band also cannot conduct a current. This follows from the fact that no two electrons can simultaneously occupy the same quantum state. The general formal statement of this is the Pauli Principle, which applies to the class of particles called fermions, and includes electrons, protons, and neutrons. The Pauli Principle plays a strong role in the formation of atoms. As the reader is aware from fundamental chemistry, each atom in the Periodic Table is formed by

**Figure 1.1** Sketch of the conduction, forbidden, and valence bands within a semiconductor. Electrons within the conduction band can freely propagate through the crystal and thus can carry a current. Electrons within the valence band are localized into bound electronic states formed by the molecular bonding of the constituent atoms of the crystal. In the forbidden band, no electronic states exist and thus electrons cannot exist within the forbidden band. The forbidden band is also called the energy gap.

progressively adding an electron and proton (and possibly neutrons) to each previous atom starting with hydrogen. In the case of hydrogen the only charged particles present are one electron and one proton. The electron is placed into the lowest lying energy state of the atom. The next element is helium which comprises two electrons and two protons as well as two neutrons. The additional electron cannot be added to the same quantum state as the first electron and is placed into the first level, 1s, but with a different spin state. The 1s level is completely filled by two electrons. Thus for the next element, lithium with three electrons and three protons plus neutrons, the third electron in lithium must go into a higher energy state than that of the first two electrons, the 2s orbital. Thus ever larger atoms containing more electrons and protons are configured such that the additional electrons enter higher energy states. If electrons did not obey the Pauli Principle, then all of the electrons in an atom, no matter how many electrons are present, would be put into the lowest energy, 1s state. As a result, chemistry would be very different from what is observed.

According to the Pauli Principle, an electron cannot move into an already occupied state. This situation is similar to that of parking automobiles in a parking lot. No two cars can be put into the same parking spot simultaneously. Obviously, a parking spot must initially be unoccupied in order to place a car into it. Electrons behave in much the same way. In the case of electrons, quantum states assume the same role as parking spaces do for cars. It is important to further recognize that a filled parking lot cannot accept any more cars without removing one and similarly a filled energy band cannot accept any more electrons without removing one. Now we can understand why a filled energy band does not conduct a current. For a current to flow, electrons must move from one state to another. In a filled band there are no vacancies into which the electrons can move since all possible states are filled. Hence, no current can flow.

The distinction among each of the four categories of solids can now be made based on the energy bands in the material. An insulator is a material in which the highest occupied band, called the valence band, is completely filled and the next available energy band, called the conduction band, is completely empty. The energy separation between the filled and empty bands is called the energy gap. In order for a material to be insulating, it is also necessary that the energy gap be very high such that carriers cannot be readily promoted from the valence band into the conduction band. Therefore in an insulator, the valence band is completely filled and the conduction band is completely empty and no current can flow in the material. Conversely, a metal is a highly conductive material. Metals are solids in which the conduction band is only partially filled. The conduction band consists then of many electrons and many empty states. A large current can be supported within a metal since most of the electrons within the conduction band can contribute to the current conduction since there exist many vacancies into which the electrons can move under the action of a driving field. Consequently, metals have a very high electrical conductivity. The other two categories of materials, semimetals and semiconductors, are somewhat intermediate between metals and insulators. Semimetals are materials like insulators in that the conduction band is unoccupied and the valence band is fully occupied at zero temperature. However, in semimetals the energy gap vanishes in part such that the conduction and valence bands intersect. Electrons from the valence band can be readily accelerated into the conduction band at the point or points of intersection of the two bands and the material can thus support a current. In this way, semimetals exhibit a relatively high conductivity but not as high as that of a metal. Finally, a semiconductor is something like an insulator but with a relatively small energy gap separating the conduction and valence bands. At absolute zero temperature within a semiconductor the conduction band is completely empty and the valence band is completely filled. However, as the temperature is raised to room temperature, the energy gap is sufficiently small that some measurable population of the conduction band occurs. Therefore, a semiconductor will conduct a current at room temperature but with a much higher resistance than that of a metal.

The electrical resistance of a crystal is a function of the electron concentration in the conduction band. In a metal, the electron concentration within the conduction band is extremely high, on the order of  $\sim 10^{23}$  cm<sup>-3</sup>. In a semiconductor the electron concentration within the conduction band is many orders of magnitude lower. Therefore, the conductivity of a semiconductor is much less than that of a metal. To quantify the conductivity it is essential to determine the electron concentration. In the next section the technique used to determine the electron concentration within a semiconductor will be discussed.

Before we end this section, it is useful to discuss the shape of the energy bands in a crystal. One of the basic concepts of quantum mechanics is that fundamental particles have a wave-particle duality. This implies that a fundamental particle like an electron for example sometimes manifests itself as a wave and sometimes as a particle, but never simultaneously. Therefore, an electron has a wavelength associated with it, called the de Broglie wavelength, that accounts for its wavelike behavior. The momentum of an electron can be described using its wavelike behavior as

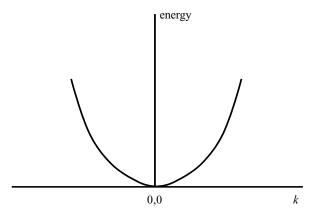

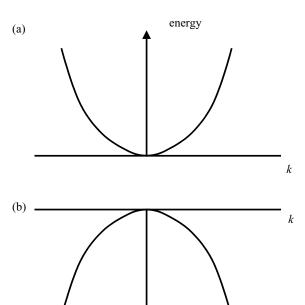

**Figure 1.2** Sketch of the energy vs. *k* relationship for free electrons. Energy bands that obey this relationship are called parabolic energy bands. To a good approximation the energy bands within a semiconductor, at least near the band edge (bottom of the conduction band and top of the valence band), are parabolic.

$$p = \hbar k \tag{1.1}$$

where  $\hbar$  is Planck's constant divided by  $2\pi$  and k is defined as

$$k = \frac{2\pi}{\lambda} \tag{1.2}$$

$\lambda$  is the electron wavelength and k is called the electron wavevector. A free electron has only kinetic energy given by

$$E = \frac{p^2}{2m} \tag{1.3}$$

Substituting into (1.3) for p the expression given by (1.1) obtains

$$E = \frac{\hbar^2 k^2}{2m} \tag{1.4}$$

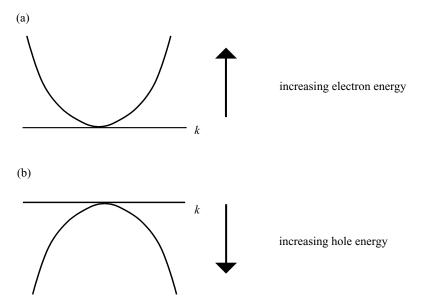

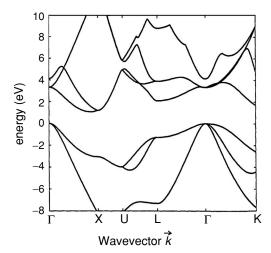

The energy of the electron varies quadratically with the wavevector, k. The relationship between E and k given by (1.4) is called a parabolic energy vs. k relationship and is sketched in Fig. 1.2. Notice that the energy vs. k diagram shown in Fig. 1.2 is a parabola with vertex at E=0, k=0. Since the electron energy varies with respect to the electron wavevector, the E(k) relationship is very important in semiconductors. The behavior of the electron as a function of k is referred to as the electron motion in k-space. In general, the wavevector  $\vec{k}$  for an electron in a crystal is a three-dimensional vector. In free space, we can replace the vector  $\vec{k}$  by its one-dimensional scalar magnitude, k. We can also often use this scalar one-dimensional model to gain insight into the behaviour of an actual semiconductor.

Typically, the mass that appears in the denominator of (1.4) is quite different from the free space mass and is referred to as the effective mass, usually written as  $m^*$ . The effective mass is usually less than the free space mass and takes into account

the motion of the electron within the crystalline lattice. The electron effective mass is defined as

$$\frac{1}{m^*} = \frac{1}{\hbar^2} \frac{d^2 E}{dk^2} \tag{1.5}$$

Notice that (1.5) implies that the curvature of the E(k) relationship determines the effective mass of the electron. If the curvature is high, meaning that E changes greatly with a small change in k, then the effective mass of the electron is small. Conversely, if the curvature is low, implying that the energy E changes slowly with change in k, then the effective mass of the electron is large. In the limit of a horizontal line in the E(k) relationship, the effective mass is infinite; the energy never changes for any change in momentum or k.

The energy bands within most semiconductors deviate from the simple parabolic energy relationship given by (1.4) at high energy, defined as several kT above the conduction band minimum or edge or several kT below the valence band edge. The valence band edge is the point of minimum hole energy within the valence band and typically lies at k=0 in k-space. The energy band structure in general is very complicated in most semiconductors, yet can have a profound effect on device operation, as will be seen in later chapters.

### 1.2 Equilibrium carrier concentrations and intrinsic material

It is important first to understand the concept of equilibrium. A full discussion of equilibrium can be found in the book by Brennan (1999). The most exacting definition of a system in equilibrium is that a closed system, isolated from the external environment, if left to itself over time will evolve towards equilibrium. Under equilibrium conditions there are no external agents, i.e., external voltages, external fields, radiative excitations, or any other external perturbation acting on the system. The system is completely isolated from the external world and as such is unperturbed. There is an important difference between equilibrium and steady-state. In steady-state the system does not change with time, but it is not isolated from the external world. In equilibrium the system is completely isolated from the external world and thus does not change with time but also has no net current flow. A system in steady-state though it does not change with time still has a net current flow. One simple way to view the difference between equilibrium and steady-state is to imagine a partially filled sink. In equilibrium the water level does not change and remains constant. Additionally, there is no net current flow. There is no input or output of water from the sink, the faucet is off and the drain is closed. For a sink in steady-state the water level also doesn't change. However, there is a net current flow. The faucet is on and the drain is open such that the input matches the output and thus the water level does not change. However, the

<sup>&</sup>lt;sup>†</sup> Here,  $k = k_B$ , Boltzmann's constant. It is usually multiplied by T, the absolute temperature. The factor kT appears in the Fermi–Dirac distribution function, discussed in Section 1.2.

system interacts with its external environment and thus is not in equilibrium but in steady-state instead.

In order to calculate the electron concentration within the conduction band of a semiconductor in equilibrium it is useful to again draw an analogy to parking spaces and cars. In order to park one's car two conditions must be met. First, there must be a parking space. One cannot park one's car, at least legally and safely, in the middle of the road. There must be a parking space. However, the mere presence of a parking space does not ensure that one can park one's car. The second condition is that the space must be unoccupied. The obvious statement that one must have a vacant parking space available to park one's car has an analogy for electrons. In order to put an electron into an energy state, a similar set of two conditions must exist. These are that there must exist a state matching the energy of the electron into which it can be put and this state must be unoccupied. The total number of electrons in the conduction band depends upon the number of available states at a given energy multiplied by the probability that each state is occupied. Summing this product over all possible energies will give the total number of electrons within the conduction band. Mathematically, we can determine the electron concentration in the conduction band by integrating the product of the function that describes the number of available states at a given energy, called the density of states, D(E), and the function that gives the probability that a state at that energy will be occupied, called the distribution function, f(E). The electron concentration, n, is given then as

$$n = \int D(E)f(E)dE \tag{1.6}$$

where the integration is taken over the full range of energy values. In order to evaluate this expression it is necessary to determine both D(E) and f(E). The density of states function D(E) for a three-dimensional system is given as (Brennan, 1999, Section 5.1),

$$D(E) = \frac{1}{2\pi^2} \left(\frac{2m}{\hbar^2}\right)^{\frac{3}{2}} \sqrt{E}$$

(1.7)

where  $\hbar$  is the reduced Planck constant,  $h/2\pi$ .

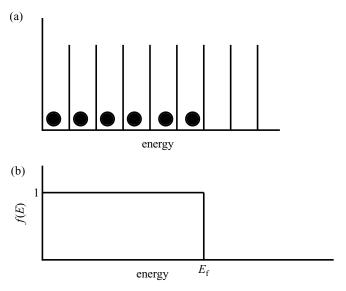

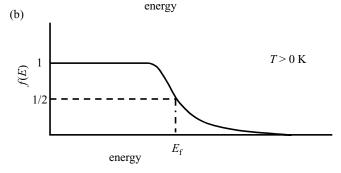

The probability distribution function, f(E), depends upon whether the system is in equilibrium or not. What then is the form of the equilibrium probability distribution function for electrons? To answer this question let us consider Fig. 1.3. Figure 1.3 shows a collection of bins, arranged in ascending energy into which one can place an electron. Let each bin represent an allowed energy state. It is important to recall that no two electrons can occupy the same quantum state simultaneously in accordance with the Pauli Principle. Therefore, once an electron has been placed into a bin, no additional electrons can be put into that bin. To attain the minimum energy configuration of the system the first electron must be put into the first bin. The next electron must then be placed into the second bin, the third electron into the third bin and so forth. This process continues until all of the electrons are placed into the first six bins as shown in the diagram. The normalized probability of each of the first six

**Figure 1.3** (a) Collection of energy bins representing energy states arranged in ascending energy. Into each bin only one electron can be placed in accordance with the Pauli Principle. Each circle represents an electron. The figure shows the minimum energy configuration of an arrangement of six electrons. (b) Corresponding probability distribution function, f(E).

bins being occupied is thus 1. All bins above the sixth bin are empty in the example since no additional electrons are present. Hence the normalized probability of the bins higher than six being occupied is zero. The resulting probability distribution function is shown in Fig. 1.3(b). Note that the probability distribution shown in Fig. 1.3(b) holds for T = 0 K. Clearly, the probability distribution function reflects the physical situation, each of the first six states or bins is occupied, while those above six are empty. Inspection of Fig. 1.3 shows that the distribution has the value of 1 until an energy,  $E_{\rm f}$ , is reached. This energy is called the Fermi level and is related to the number of electrons present in the system. For the present example, the energy corresponding to the Fermi level lies at the energy corresponding to the sixth bin.

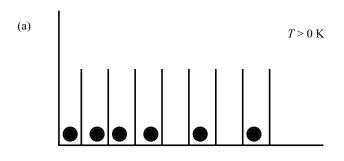

What happens though at temperatures greater than absolute zero? Temperature is a measure of the internal energy of the system. At temperatures greater than zero, the total energy of the system must be greater than that corresponding to T=0 K. Let us again consider a system with only six electrons. For simplicity let us set the energy of each bin to be an integer multiple of E. Thus for the system shown in Fig. 1.3(a), the total energy is given as the sum of the occupied bins as E+2E+3E+4E+5E+6E=21E. The next highest energy configuration, or higher temperature of the system is obtained by promoting the sixth electron into the seventh bin. The corresponding energy of the resulting configuration is then equal to E+2E+3E+4E+5E+7E=22E, which is obviously higher than that of the E=0 K configuration. Higher temperature configurations are similarly achieved, i.e. by promoting electrons from the lower energy states into higher energy states. An example system is shown

**Figure 1.4** (a) Distribution of a collection of six electrons in energy bins corresponding to a collective energy or temperature greater than 0 K. (b) Corresponding probability distribution function for a T > 0 K distribution.

in Fig. 1.4 along with the corresponding probability distribution function. As can be seen from the figure, at higher energies there exists a tail in the distribution function. This implies that there is a nonzero probability of a state with energy greater than  $E_{\rm f}$  being occupied and correspondingly a nonzero probability that states below  $E_{\rm f}$  are unoccupied.

The equilibrium probability distribution function, f(E), called the Fermi–Dirac distribution can be expressed mathematically. Its derivation is rather complicated and will not be repeated here. The interested reader is referred to the books by Brennan (1999, Chapter 5) or Kittel and Kroemer (1980). The Fermi–Dirac distribution is given

$$f(E) = \frac{1}{1 + e^{\frac{(E - E_f)}{kT}}}$$

(1.8)

where k is Boltzmann's constant.

It is instructive to examine how f(E) behaves and to show it replicates the distributions shown in Figs. 1.3 and 1.4. Consider first its behavior at T=0 K. There are two conditions,  $E < E_{\rm f}$  and  $E > E_{\rm f}$ . For  $E < E_{\rm f}$ , the exponent in (1.8) is negative infinity (due to the division by zero), and exp of negative infinity is zero. Thus f(E) for  $E < E_{\rm f}$ , is 1/(1+0) or simply 1. This is of course exactly what is expected; for energies less than the Fermi level, at T=0 K, f(E)=1. The second case,  $E > E_{\rm f}$  at T=0 K leads to the following. Notice that in this case, the exponent is now positive infinity,

and exp of positive infinity is infinity. Thus the denominator of (1.8) becomes infinity and  $f(E) = 1/\infty = 0$ . Again this is consistent with Fig. 1.3; for energies greater than  $E_{\rm f}$  at T = 0 K, f(E) = 0. At energy  $E = E_{\rm f}$ , the Fermi–Dirac function has value  $\frac{1}{2}$  as is readily seen from (1.8).

For temperatures greater than 0 K, f(E) is no longer a simple step function and has a tail as shown in Fig. 1.4. If we consider the situation where E is large, such that  $e^{(E-E_f)/kT} \gg 1$ , then f(E) can be approximated as

$$f(E) = \frac{1}{1 + e^{\frac{(E - E_f)}{kT}}} \sim \frac{1}{e^{\frac{(E - E_f)}{kT}}} \sim e^{-\frac{(E - E_f)}{kT}}$$

(1.9)

Under this condition, the Fermi–Dirac distribution behaves as the Maxwell–Boltzmann distribution, and clearly the occupation probability of a state of energy *E* decreases exponentially with increasing energy. This is as it should be since few electrons, if any, will occupy very high energy states.

At this point, we can now determine the equilibrium electron concentration in a semiconductor using (1.6) by substituting in for D(E) and f(E) the expressions given by (1.7) and (1.8). The general expression, valid for all possibilities, involves using the Fermi–Dirac distribution for f(E). However, this choice of f(E) necessitates that the integral in (1.6) be solved numerically. Alternatively a closed form solution can be obtained if the distribution function f(E) is approximated by the Maxwell–Boltzmann distribution as

$$f(E) \sim e^{-\frac{(E-E_f)}{kT}} \tag{1.10}$$

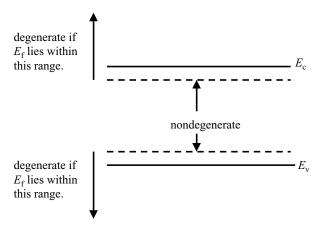

Usage of the Maxwell–Boltzmann distribution for f(E) holds when the Fermi level lies within the forbidden gap about 3kT below the conduction band edge or 3kT above the valence band edge. When this condition is valid, the semiconductor is said to be nondegenerate. If the Fermi level lies close to or within the conduction or valence bands the material is said to be degenerate and the full Fermi–Dirac formulation for f(E) should be used. A degenerate material is produced by heavily doping the semiconductor. The ranges in which a semiconductor is nondegenerate and degenerate are shown in Fig. 1.5. Using the Maxwell–Boltzmann distribution the electron concentration within the conduction band can be determined from

$$n = \int_{0}^{\infty} \frac{8\pi m^{\frac{3}{2}} \sqrt{2E}}{h^{3}} e^{-\frac{(E-E_{f})}{kT}} dE$$

(1.11)

In (1.11) the lower bound on the integral is set to zero since we assume that the minimum energy is the conduction band edge. Of course, the upper limit on the energy in a realistic energy band is not infinity but the upper bound can be extended to infinity with little error since the probability distribution decreases exponentially with increasing energy. Therefore, the error introduced by integrating n(E) to infinity is exceedingly small. Equation (1.11) can be evaluated using

$$\int_{0}^{\infty} \sqrt{x} e^{-ax} dx = \frac{\sqrt{\pi}}{2a\sqrt{a}}$$

(1.12)

**Figure 1.5** Sketch of the energy bands of a semiconductor illustrating the conditions for degenerate and nondegenerate doping. Notice that a degenerate material is highly doped such that the Fermi level lies either near or above the conduction band in n-type material or near or below the valence band in p-type material.

to be

$$n = 2\left(\frac{2\pi m_{\rm e}^* kT}{h^2}\right)^{\frac{3}{2}} e^{\frac{E_{\rm f}}{kT}}$$

(1.13)

where  $m_{\rm e}^*$  is the electron effective mass. The mass of an electron within the semiconductor is not the same as in free space. Instead, the electron behaves within the crystal as if it has a different mass, called the reduced mass. The reduced mass arises from the motion of the electrons in the periodic potential of the ions forming the crystalline lattice. If we call the bottom of the conduction band  $E_{\rm c}$  instead of zero, then (1.13) becomes

$$n = 2\left(\frac{2\pi m_{\rm e}^* kT}{h^2}\right)^{\frac{3}{2}} e^{\frac{-(E_{\rm c} - E_{\rm f})}{kT}}$$

(1.14)

Defining the effective density of states,  $N_c$ , as

$$N_{\rm c} = 2\left(\frac{2\pi m_{\rm e}^* kT}{h^2}\right)^{\frac{3}{2}} \tag{1.15}$$

the value of *n* can be written as

$$n = N_{\rm c} e^{-\frac{(E_{\rm c} - E_{\rm f})}{kT}} \tag{1.16}$$

A similar expression holds for the equilibrium hole concentration within the valence band as

$$p = N_{\rm v} \mathrm{e}^{-\frac{(E_{\rm f} - E_{\rm v})}{kT}} \tag{1.17}$$

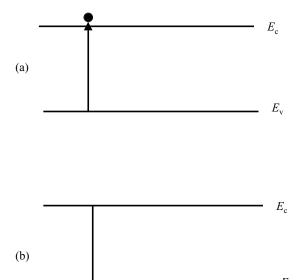

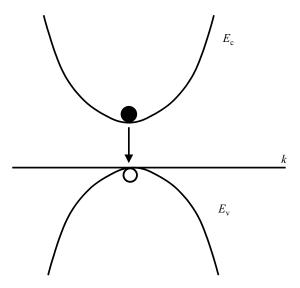

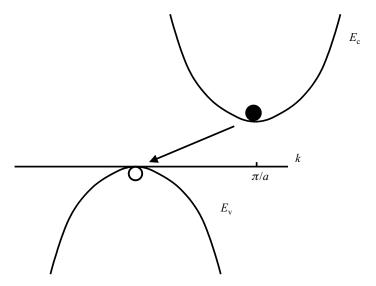

**Figure 1.6** Sketch of (a) the conduction band and (b) the valence band showing the direction of increasing electron and hole energy.

where  $N_{\rm v}$  is the same as (1.15) with the hole mass,  $m_{\rm h}^*$ , used in place of the electron mass,  $m_{\rm e}^*$ , yielding

$$N_{\rm v} = 2\left(\frac{2\pi m_{\rm h}^* kT}{h^2}\right)^{\frac{3}{2}} \tag{1.18}$$

Equations (1.16) and (1.17) apply for the electron and hole concentrations for a semi-conductor in equilibrium.

An intrinsic semiconductor has no intentionally added impurities. Conversely, an extrinsic semiconductor has intentionally added impurities called dopants. In an intrinsic semiconductor promoting electrons from the valence band produces carriers within the conduction band. The vacancies produced within the valence band from the promotion of electrons are called holes. The two most salient features of holes necessary for our discussion are that holes are positively charged and that hole energy increases downwards in the energy band diagram as opposed to electron energy which increases upwards as shown in Fig. 1.6. A hole is a vacancy within an otherwise filled band. Thus when an electron is promoted from the valence band into the conduction band a vacancy or hole is left behind in the valence band. As a result, the conduction band is no longer empty and can now conduct a current. This is obvious since there is now an electron within the band and it can move between different unoccupied energy states under the action of an applied field. Similarly, the valence band is no longer completely filled and thus it too can conduct a current. Given that there are now vacancies within the valence band, the electrons within the valence band can move from one

vacancy to the next. This movement of electrons within the nearly filled valence band is equivalent to the movement of the corresponding number of holes within an empty band, provided that the holes have opposite sign to that of the electrons. For example, if there are N-1 electrons within the valence band equivalently there is one hole. The current carrying species within the conduction band is of course the free electron that has been promoted from the valence band. The current carrying species within the valence band is the hole.

What though is the current carried by the hole? If the band is completely filled, then no current flows. The corresponding current density is given by summing over all of the electron velocities as

$$\vec{j} = -q \sum_{i=1}^{N} \vec{v}_{i} \tag{1.19}$$

For a completely filled band, as mentioned above the net current is zero. This implies that there are on average, an equal number of electrons crossing a Gaussian surface moving to the left as are moving to the right. Therefore, the net flux of electrons across the surface on average is zero. Consequently, the net average velocity of the carriers must also be zero; for every electron motion there is another electron with an opposite but equal motion. Thus the net velocity of the entire system vanishes as well as the current density. The current density corresponding to the motions of the electrons within a partially filled band can be related to the motion of the vacancies by recognizing that

$$\vec{j}_{\text{filled}} - \vec{j}_{\text{occupied}} = \vec{j}_{\text{vacancies}}$$

(1.20)

But the current density due to the filled band is zero. Consequently, the current density produced by the motion of the vacancies must be the exact negative of that produced by the motion of the electrons. The current density due to the motion of the holes (vacancies) is then

$$\vec{j} = +q \sum_{i=1}^{N} \vec{v}_{i} \tag{1.21}$$

A hole thus behaves like a positively charged particle. Hence, holes move in the opposite direction from electrons under the action of an applied field.

Within an intrinsic material the electron concentration is equal to the hole concentration, n = p. The intrinsic carrier concentration in equilibrium is called  $n_i$ . The Fermi level in intrinsic material is referred to as the intrinsic level,  $E_i$ . The position of the intrinsic level can be determined as follows. Since n = p, the equilibrium electron and hole concentrations in intrinsic material can be related as

$$N_{\rm c} e^{\frac{(E_{\rm i} - E_{\rm c})}{kT}} = N_{\rm v} e^{\frac{(E_{\rm v} - E_{\rm i})}{kT}}$$

(1.22)

where  $E_i$  has been inserted in place of  $E_f$  in (1.16) and (1.17). Solving for  $E_i$  in (1.22) obtains

$$\frac{N_{\rm v}}{N_{\rm c}} = e^{\frac{(E_{\rm i} - E_{\rm c} - E_{\rm v} + E_{\rm i})}{kT}}$$

$$E_{\rm i} = \frac{(E_{\rm c} + E_{\rm v})}{2} + \frac{kT}{2} \ln\left(\frac{N_{\rm v}}{N_{\rm o}}\right) \tag{1.23}$$

Substituting into (1.23) the relationships for  $N_{\rm v}$  and  $N_{\rm c}$  given by (1.15) and (1.18) obtains

$$E_{\rm i} = \frac{(E_{\rm c} + E_{\rm v})}{2} + \frac{3kT}{4} \ln \left( \frac{m_{\rm h}^*}{m_{\rm e}^*} \right) \tag{1.24}$$

In some materials the effective masses of the electrons and holes are roughly equal. In this case, the intrinsic level lies at midgap, halfway between the conduction and valence bands. Even if the effective masses are substantially different it is a reasonable assumption to set the intrinsic level equal to the midgap energy. For example, in GaAs the electron and hole effective masses are 0.067 and 0.62 respectively. The last term in (1.24) is equal to 0.043 eV. The midgap energy is 0.71, so we see that the correction due to the difference in the effective masses, even when they are substantially different, is small.

The intrinsic concentration,  $n_i$ , can be obtained as follows. For an intrinsic semi-conductor the electron and hole concentrations are equal:

$$n = p = n_{\rm i} \tag{1.25}$$

As we discussed above, the Fermi level,  $E_f$  can be replaced by  $E_i$  the intrinsic level. Using the above results,  $n_i$  can be written as

$$n_{i} = N_{c} e^{\frac{(E_{i} - E_{c})}{kT}}; \quad n_{i} = N_{v} e^{\frac{(E_{v} - E_{i})}{kT}}$$

(1.26)

Rearranging the terms in (1.26)  $n_i$  can be expressed as

$$N_{\rm c}e^{-\frac{E_{\rm c}}{kT}} = n_{\rm i}e^{-\frac{E_{\rm i}}{kT}} \tag{1.27}$$

The electron concentration, n, can now be expressed in terms of the intrinsic concentration using (1.27). Starting with (1.16)

$$n = N_{\rm c} e^{-\frac{E_{\rm c}}{kT}} e^{\frac{E_{\rm f}}{kT}} \tag{1.28}$$

Substituting (1.27) into (1.28) obtains

$$n = n_{\rm i} e^{\frac{(E_{\rm f} - E_{\rm i})}{kT}} \tag{1.29}$$

Similarly, the hole concentration can be written as

$$p = n_i e^{\frac{(E_i - E_f)}{kT}} \tag{1.30}$$

Equations (1.29) and (1.30) hold for a nondegenerate semiconductor in equilibrium in which approximating the Fermi–Dirac distribution by the Maxwell–Boltzmann distribution is valid.

Consider the product of n and p for an intrinsic semiconductor. Using (1.29) and (1.30) the np product is given as

$$np = n_i^2 e^{\frac{(E_i - E_j)}{kT}} e^{\frac{(E_i - E_f)}{kT}}$$

(1.31)

which is simply

$$np = n_i^2 \tag{1.32}$$

Equation (1.32) is called the Law of Mass Action. The Law of Mass Action applies only in equilibrium but it is true for any semiconductor either intrinsic or extrinsic. The np product can be written in an alternative manner using (1.16) and (1.17) as

$$n = N_{\rm c} e^{-\frac{E_{\rm c}}{kT}} e^{\frac{E_{\rm f}}{kT}} \qquad p = N_{\rm v} e^{\frac{E_{\rm v}}{kT}} e^{-\frac{E_{\rm f}}{kT}}$$

(1.33)

Taking the product of n and p given by (1.33) obtains,

$$np = N_{\rm c}N_{\rm v}e^{-\frac{(E_{\rm c}-E_{\rm v})}{kT}} = N_{\rm c}N_{\rm v}e^{-\frac{(E_{\rm g})}{kT}} = n_{\rm i}^2$$

(1.34)

where  $E_g = E_c - E_v$ , the energy difference between the top of the valence band and the bottom of the conduction band, the "gap energy" of the semiconductor. Substituting in for  $N_c$  and  $N_v$  we finally obtain for  $n_i$

$$n_{\rm i} = \frac{2}{h^3} (2\pi kT)^{\frac{3}{2}} (m_{\rm e}^* m_{\rm h}^*)^{\frac{3}{4}} e^{-\frac{E_{\rm g}}{2kT}}$$

(1.35)

which is a constant.

#### 1.3 Extrinsic material

A semiconductor into which impurities, called dopants, are intentionally added in order to alter the conductivity of the sample is said to be extrinsic. There are two dopant types. These are n-type dopants called donors and p-type dopants called acceptors. In a semiconductor doped with donors the equilibrium electron concentration becomes larger than the equilibrium hole concentration and the semiconductor is said to be n-type. Similarly, if the semiconductor is doped with acceptors, the equilibrium hole concentration is greater than the equilibrium electron concentration and the semiconductor is said to be p-type.

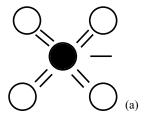

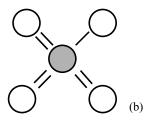

An example donor atom in silicon is phosphorus. Phosphorus is a Column VA element while silicon is a Column IVA element. Therefore, phosphorus has an outer valence of five while silicon has an outer valence of four. Silicon crystallizes such that each silicon atom forms bonds with four other silicon atoms fully accommodating all four outer valence electrons. If a phosphorus atom is substituted for a silicon atom in an otherwise silicon lattice, then one of the outer valence electrons within the phosphorus atom is not bound to a neighboring silicon atom as shown in Fig. 1.7(a). The phosphorus atom then only weakly holds the unbound electron. The other four valence electrons in phosphorus are chemically bound to four neighboring silicon

**Figure 1.7** (a) A two-dimensional representation of a donor atom, phosphorus, shown in black, within a silicon matrix. Each silicon atom is represented by an open circle. Each line represents an outer valence electron. Notice that the extra electron in the outer shell of the phosphorus atom is unbound. (b) A two-dimensional representation of an acceptor atom, boron, shown in gray, within a silicon matrix. Each silicon atom is again represented by an open circle. Notice that one of the bonds is not filled yielding a hole.

atoms. The unbound electron can be readily ionized since it is not chemically bound. Once ionized, the unbound electron can move freely through the crystal and thus lies within the conduction band.

p-type doping can be achieved by adding an atom with fewer electrons in the outer shell than silicon. An example of a p-type dopant is aluminum. Aluminum is a Column IIIA element and as such has only three electrons in its outermost atomic orbital. If an atom of aluminum substitutes for an atom of silicon within the silicon matrix, one of the four bonds to the nearest neighbor atoms is unfilled as shown in Fig. 1.7(b). The vacant bond is called a vacancy or a hole. The vacancy can propagate through the lattice as a result of electrons jumping from one occupied state into another, each time leaving a vacancy behind.

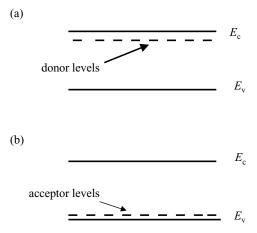

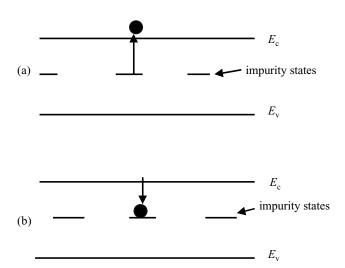

It is useful to picture the donor and acceptor states in an energy level diagram. The key to understanding the energy level diagrams for donors and acceptors is to recognize that the donor and acceptor states, being impurity states, lie somewhere between the conduction and valence bands of the host semiconductor material. Donor and acceptor atoms are special types of impurities in that they introduce levels near the conduction and valence band edges respectively as shown in Fig. 1.8. Deep levels formed by impurity atoms added to the host semiconductor cannot easily be ionized. As a result these levels act as traps. The energy levels in this case lie near midgap and thus require extensive energy in order to be ionized.

**Figure 1.8** Sketch of the energy band diagrams of a semiconductor doped with (a) donors and (b) acceptors. Notice that the donor and acceptor atoms lie near the conduction and valence band edges respectively. Therefore, only a small amount of energy is needed to ionize either dopant.

In Section 1.2 we found that the electron and hole concentrations can be written in terms of the intrinsic level and Fermi level as

$$n = n_i e^{\frac{(E_f - E_i)}{kT}}$$

$p = n_i e^{\frac{(E_i - E_f)}{kT}}$  (1.36)

The position of the Fermi level with respect to the intrinsic level determines the doping type in the semiconductor. Notice that the product of n and p once again yields the Law of Mass Action.

To decide if a semiconductor is n- or p-type it is necessary to compare the electron and hole concentrations with the intrinsic concentration. To do this the charge neutrality condition must be invoked. The charge neutrality condition is given as

$$0 = p - n + N_{\rm d}^{+} - N_{\rm a}^{-} \tag{1.37}$$

Equation (1.37) implies that the net charge within the semiconductor is zero. The net positive charge contributed by the holes and ionized donors is balanced by the net negative charge contributed by the electrons and ionized acceptors. In most situations, only one ionized dopant atom dominates, either the donors or acceptors. Consider first an intrinsic semiconductor. In an intrinsic semiconductor the donor and acceptor concentrations are zero. Thus (1.37) becomes

$$0 = p - n \tag{1.38}$$

which of course is simply p = n. Alternatively for extrinsic material if  $N_d \gg N_a$  then the material is n-type. Under this assumption, the acceptor concentration can be neglected with respect to the donor concentration. The electron concentration can be determined as follows. The charge neutrality condition becomes

$$0 = p - n + N_{\rm d}^{+} \tag{1.39}$$

The hole concentration can be expressed in terms of n using the Law of Mass Action (equilibrium conditions) as

$$p = \frac{n_{\rm i}^2}{n} \tag{1.40}$$

Substituting (1.40) into (1.39) obtains

$$\frac{n_{\rm i}^2}{n} - n + N_{\rm d} = 0 \tag{1.41}$$

Equation (1.41) is simply a quadratic equation in n given as

$$n^2 - N_{\rm d}n - n_{\rm i}^2 = 0 ag{1.42}$$

It can be solved as

$$n = \frac{N_{\rm d} \pm \sqrt{N_{\rm d}^2 + 4n_{\rm i}^2}}{2} \tag{1.43}$$

Notice that if  $n_i \ll N_d$  then (1.43) simplifies to

$$n = N_{\rm d} \tag{1.44}$$

Similarly, if  $N_a > N_d$  and  $n_i \ll N_a$  then we obtain

$$p = N_a \tag{1.45}$$

and of course the material is p-type.

If the condition given by (1.44) holds then the Fermi level can be calculated as follows. The electron concentration in n-type material is given as

$$n = N_{\rm d} = n_{\rm i} e^{\frac{(E_{\rm f} - E_{\rm i})}{kT}} \tag{1.46}$$

Solving for  $E_f$  obtains

$$E_{\rm f} = E_{\rm i} + kT \ln \left(\frac{N_{\rm d}}{n_{\rm i}}\right) \tag{1.47}$$

for n-type material. Notice that the Fermi level in n-type material is greater than the intrinsic level. Similarly, for p-type material the Fermi level is given as

$$E_{\rm f} = E_{\rm i} - kT \ln \left(\frac{N_{\rm a}}{n_{\rm i}}\right) \tag{1.48}$$

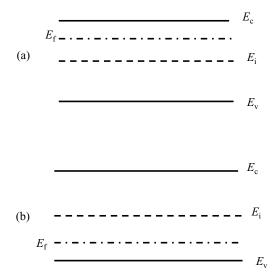

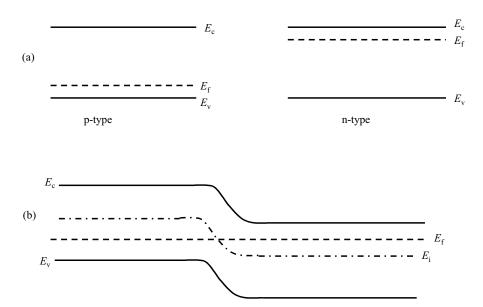

In this case the Fermi level lies below the intrinsic level. Thus for n-type material the Fermi level lies above the intrinsic level and in p-type material the Fermi level lies below the intrinsic level as shown in Fig. 1.9.

# **Example Problem 1.1**

Consider a silicon sample doped with donors at  $1\times10^{17}~\rm cm^{-3}$ . If the intrinsic concentration within silicon is  $1.0\times10^{10}~\rm cm^{-3}$ , determine the location of the Fermi level relative to the valence band.

**Figure 1.9** Sketch of the band structure showing the intrinsic level. In (a) the material is n-type since the Fermi level lies above the intrinsic level. In (b) the material is p-type since the Fermi level lies below the intrinsic level.

Since the donor doping concentration is very much larger than the intrinsic concentration, using the approximation that the electron concentration is equal to the donor concentration is valid. Therefore, the Fermi level relative to the intrinsic level is given as

$$E_{\rm f} = E_{\rm i} + kT \ln \left( \frac{N_{\rm d}}{n_{\rm i}} \right)$$

Substituting in for each term, kT = 0.0259 eV at 300 K, the Fermi level becomes

$$E_{\rm f} = E_{\rm i} + 0.417 \, {\rm eV}$$

By evaluating  $E_i$ , the position of the intrinsic level relative to the valence band can be determined.  $E_i$  is given in the text as

$$E_{\rm i} = \frac{(E_{\rm c} + E_{\rm v})}{2} + \frac{3kT}{4} \ln \left( \frac{m_{\rm h}^*}{m_{\rm s}^*} \right)$$

The effective masses in silicon for holes and electrons are

$$m_e^* = 0.328$$

$m_h^* = 0.55$

With these values for the effective masses the intrinsic level relative to the valence band edge is

$$E_{\rm i} = \frac{1.12}{2} \,\text{eV} + 0.01 \,\text{eV} = 0.57 \,\text{eV}$$

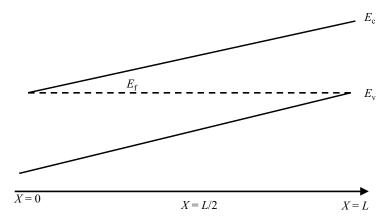

**Figure 1.10** Energy band diagram as a function of position. L is the total length of the sample.  $E_{\rm f}$  corresponds to the flat dashed line in the figure.

Thus the Fermi level is located at 0.57 eV + 0.417 eV or 0.987 eV above the valence band edge.

# **Problems**

- 1.1 Show that the probability that a state  $\Delta E$  above the Fermi level,  $E_f$ , is filled is equal to the probability that a state  $\Delta E$  below the Fermi level,  $E_f$ , is empty.

- 1.2 Determine the position of the Fermi level relative to the intrinsic level in silicon at 300 K if the electron concentration is  $1 \times 10^{16}$  cm<sup>-3</sup>. Use  $n_i = 1.0 \times 10^{10}$  cm<sup>-3</sup>.

- 1.3 (a) Show that the minimum conductivity of a semiconductor sample occurs when

$$n_0 = n_{\rm i} \sqrt{\frac{\mu_{\rm p}}{\mu_{\rm n}}}$$

- (b) What is the expression for the minimum conductivity,  $\sigma_{\min}$ ?

- (c) Calculate  $\sigma_{min}$  for Si at 300 K and compare with the intrinsic conductivity.

$$\mu_{\rm n} = 1350 \text{ cm}^2/(\text{V s})$$

$\mu_{\rm p} = 480 \text{ cm}^2/(\text{V s})$   $n_{\rm i} = 1.0 \times 10^{10} \text{ cm}^{-3}$ .

- 1.4 What are the equilibrium concentrations of electrons and holes at T = 300 K in:

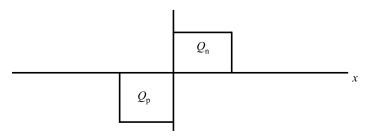

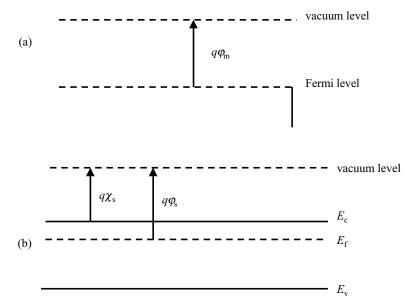

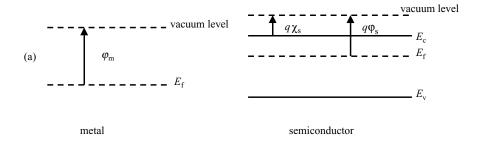

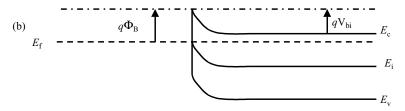

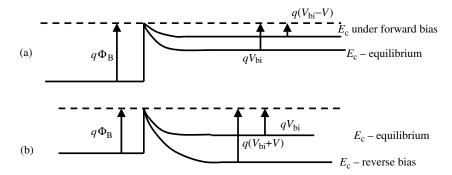

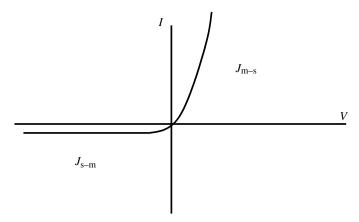

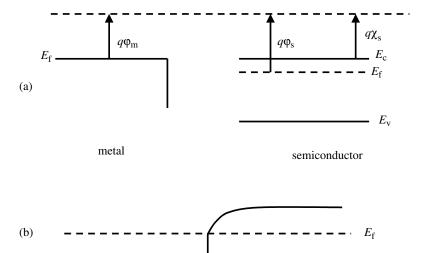

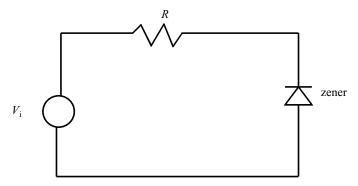

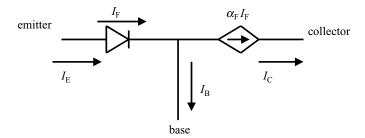

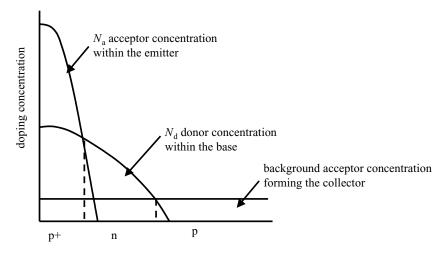

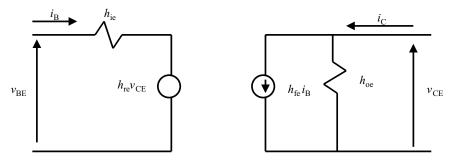

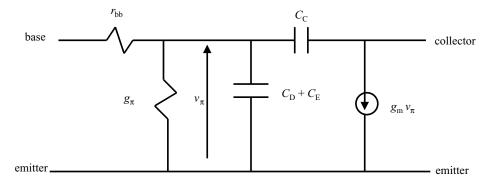

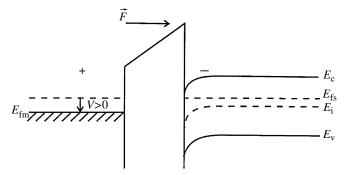

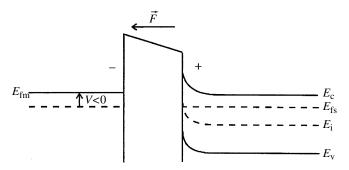

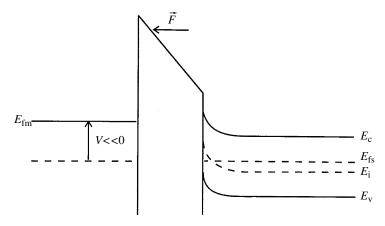

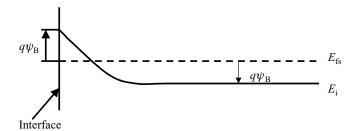

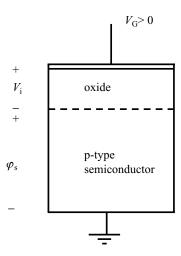

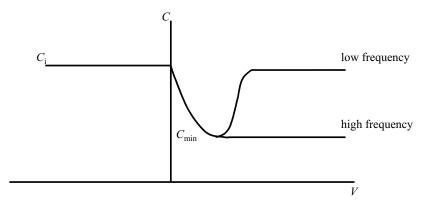

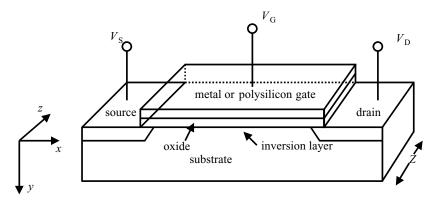

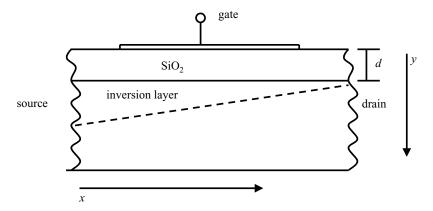

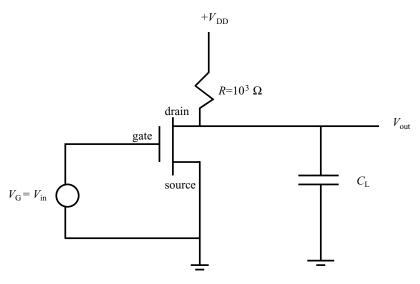

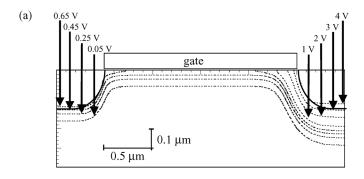

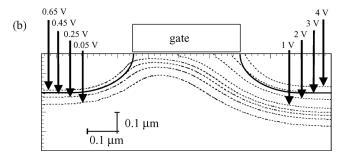

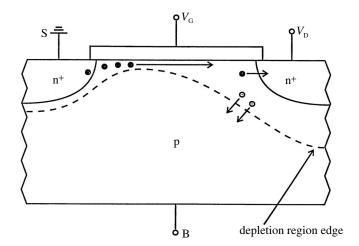

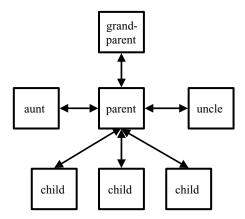

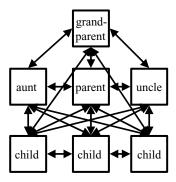

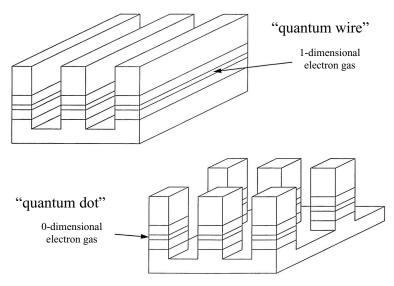

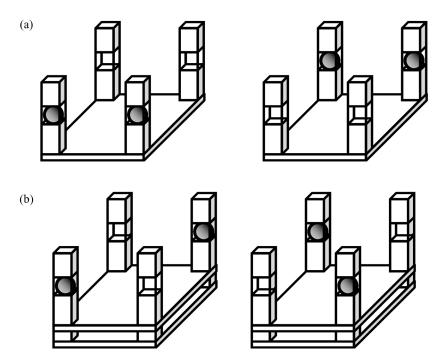

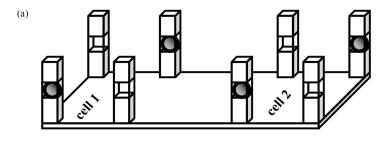

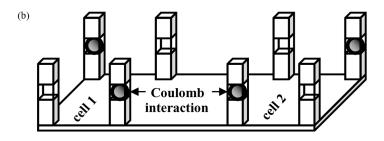

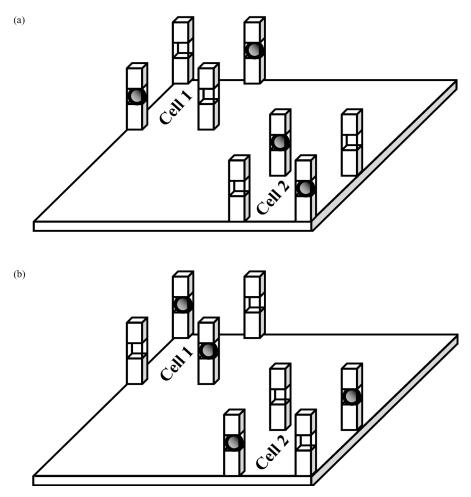

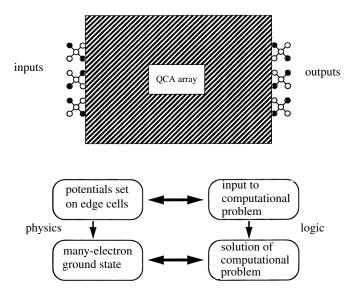

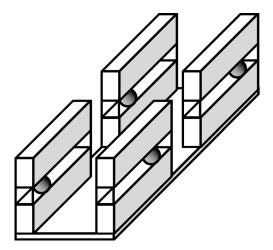

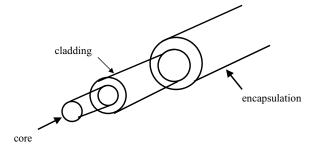

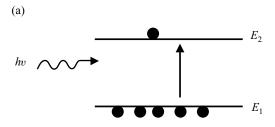

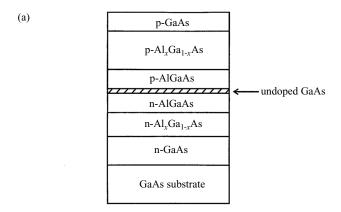

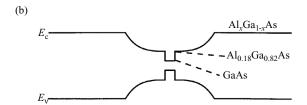

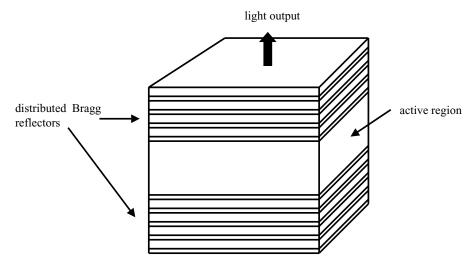

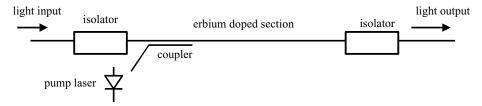

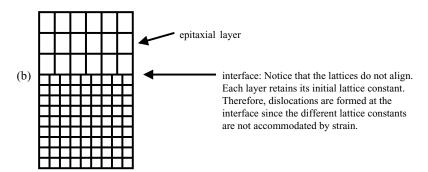

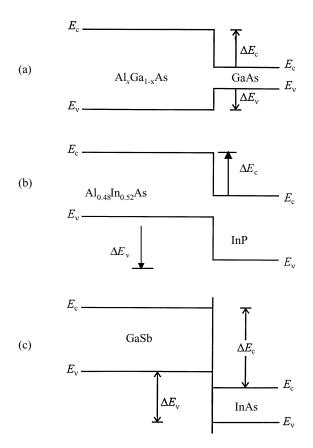

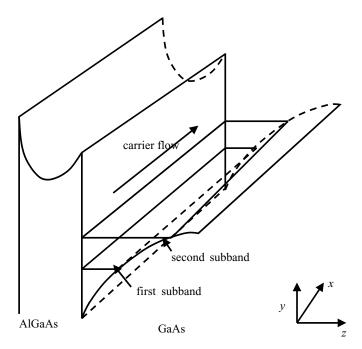

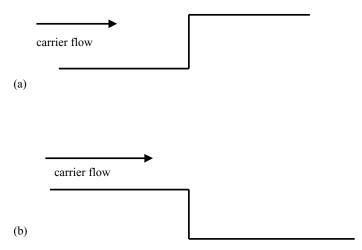

- (a) Si doped with  $N_{\rm d} = 3 \times 10^{14} \, {\rm cm}^{-3}$ ;